2. Alat dan Bahan

[Kembali]

3. Rangkaian Simulasi

[Kembali]

4. Prinsip Kerja Rangkaian

[Kembali]

1. Rangkaian Sederhana 1 : B= 0, D=1, A=1, C’=1, D= Pada rangkaian ini, digunakan 5 saklar SPDT sebagai input yang terhubung dari sumber ke gerbang logika dan ground yang mana digunakan 3 gerbang logika yaitu AND, XOR, dan, OR. dimana gerbang AND bekerja dengan mengalikan seluruh masukan, gerbang XOR akan berlogika 1 ketika ada perbedaan dari inputan dan gerbang OR dengan cara menambahkan inputan. Pada rangkain di atas B dan D terhubung ke gerbang logika XOR yang nilai input nya 0 dan 1 maka menghasilkan output bernilai 1 karena input nya berjumlah ganjil. Lalu pada gerbang logika AND menerima input dari A, C' dan D yang mana nilai input nya 1, 1 dan 1 jika di AND kan maka didapat output bernilai 1 (1x1x1). Lalu output dari XOR dan AND mengalir ke gerbang logika OR yang mana nilai input nya 1 dan 1, maka output pada OR nilainya 1 (1+1). Sehingga pada rangkaian didapatkan Output bernilai 1.

2.Rangkaian Sederhana 2 : B= 1, D=0, A= 1, B=1, C’=1Pada rangkaian ini, digunakan 5 saklar SPDT sebagai input yang terhubung dari sumber ke gerbang logika dan ground yang mana digunakan 3 gerbang logika yaitu AND, XOR, dan, OR. dimana gerbang AND bekerja dengan mengalikan seluruh masukan, gerbang XOR akan berlogika 1 ketika ada perbedaan dari inputan dan gerbang OR dengan cara menjumlahkan inputan. Pada rangkain di atas B dan D terhubung ke gerbang logika XOR yang nilai input nya 1 dan 0 maka menghasilkan output bernilai 1 karena input nya berjumlah ganjil. Lalu pada gerbang logika AND menerima input dari A, C' dan D yang mana nilai input nya 1, 1 dan 1 jika di AND kan maka didapat output bernilai 1 (1x1x1). Lalu output dari XOR dan AND mengalir ke gerbang logika OR yang mana nilai input nya 1 dan 1, maka output pada OR nilainya 1 (1+1). Sehingga pada rangkaian didapatkan Output bernilai 1.

5. Video Rangkaian

[Kembali]

6. Analisa [Kembali]

1. Bagaimana pengaruh perubahan nilai Kapasitor dan resistor? jelaskan beserta rumus.

jawab :

Berdasarkan Rumus

tn = In (a). (R1+ Rp) (c)

Diketahui bahwa t sebanding dengan C dan t juga sebanding/ berbanding lurus dengan resistor. Yakni apabila kapasitor besar maka akan semakin lama waktu yang dibutuhkan untuk pindah dan logika satu ke logika lain. Begitu pula dengan resistor. Jika resistor besar maka waktu yang dibutuhkan akan semakin lama.

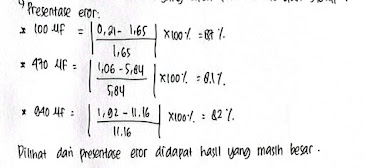

2. Analisa dan bandingkan hasil jurnal yang didapatkan di pratikum dengan hasil jurnal perhitungan. Carilah presentase errornya.

Jawab :

Rmin tidak terlalu jauh hasilnya, tetapi untuk c = 940 uf terdapat perbedaan pada perhitungan nilai besar sedangkan jurnal waktu nya sangat sebentar. Karena ini dipengaruhi oleh paralelnya kapasitor.

Rmax ada perubahan waktu yang apat pada C=470 uf dan 970 uf.

Link HTML di sini

Link Video di sini

Tidak ada komentar:

Posting Komentar